Fターム[2G132AA00]の内容

電子回路の試験 (32,879) | 試験対象 (5,171)

Fターム[2G132AA00]の下位に属するFターム

論理回路 (2,000)

アナログデジタル混在回路(AD変換器等) (239)

アナログ回路 (164)

ASIC (97)

マルチチップモジュール (163)

機能ブロック(マクロセル)を有するもの (200)

バッファ (73)

ICカード等 (26)

実装基板 (349)

Fターム[2G132AA00]に分類される特許

41 - 60 / 1,860

半導体装置

【課題】 電源遮断機能を有する半導体装置において試験用パッドを設けることなく電源ショート試験の実施を可能にする。

【解決手段】 半導体装置は、回路ブロックと、第1電源線と回路ブロックに電源電圧を供給する第2電源線との間に設けられる第1スイッチと、第1電源線と第2電源線との間に設けられる第2スイッチとを備え、第1スイッチは、テストモード時にオンし、第2スイッチは、テストモード時にオフし、第2スイッチのオン/オフに応じて、通常動作モード時に、回路ブロックの動作状態がオン/オフする。

(もっと読む)

半導体製品評価装置

【課題】後段の組立行程へ影響を与えることなく精度の高い評価結果を容易に得られる半導体製品評価装置を得ること。

【解決手段】溝13が設けられた傾斜面20aと、溝13内に配置されたリードレスパッケージの滑落を予め定められた評価位置で停止させるストッパとを備えたベース20と、先端部にソケットコンタクト6が設けられた信号導体と、先端部に信号導体の両側を挟むGND接点7が設けられた接地導体とを備え、常態ではソケットコンタクト6及びGND接点7がベース20から離間するように付勢されている一対のケーブル4と、ケーブル4をベース20側に移動させて、評価位置に配置されたリードレスパッケージの入出力電極パターンとソケットコンタクト6とを接触させ、ベースプレートとGND接点7とを接触させるケーブル押し下げ機構12とを有する。

(もっと読む)

評価試験装置および評価試験方法

【課題】時間的に連続した負荷を被試験体に印加して、被試験体の試験を行うことを可能とする、評価試験装置および評価試験方法を提供する。

【解決手段】評価試験装置は、複数の外付端子を有するデバイス(被試験体)の前記複数の外付端子それぞれに、試験負荷信号を印加する複数の第1のバッファアンプを備えている。また、前記複数の外付端子の負荷状態をそれぞれ測定して測定結果信号として出力する複数の第2のバッファアンプを備えている。さらに、前記複数の第1のバッファアンプから前記試験負荷信号を印加させながら、前記複数の第2のバッファアンプを順次駆動して前記測定結果信号を出力させるよう制御する制御手段を備えている。

(もっと読む)

半導体試験装置

【課題】テストプログラムの作成変更修正が効率よく行える半導体試験装置を提供すること。

【解決手段】所望の画面を選択するためのタブが設けられた画面を表示する表示部を有し、テストプログラムを作成変更修正するエディタと、このエディタで作成変更修正されたテストプログラムを解析する構文解析部と、この構文解析部の解析結果に基づき各種のマトリクス表示のGUI画面を編集作成するGUI画面編集部と、前記構文解析部の解析結果および前記GUI画面編集部で編集作成されたGUI画面に基づきデータ検索用一覧表を作成格納するインデクサとを具備し、前記インデクサのデータ検索用一覧表を介して、前記GUI画面におけるマトリクス表示の各交点を前記テストプログラムの構成要素にリンクさせることを特徴とする半導体試験装置である。

(もっと読む)

半導体試験装置および半導体試験装置のユニット接続方法

【課題】各ユニットを接続するシーケンスを再開するときに、メモリに記憶された情報を使用することなく、シーケンスを再開できる半導体試験装置を提供する。

【解決手段】テストヘッドとベースユニットとの間およびベースユニットとプローブカードとの間を接続して構成する半導体試験装置であって、テストヘッドとベースユニットとの間を接続してロックする第1のロック機構10のロック状態を検出するアンロック側センサ20およびロック側センサ21と、ベースユニットとプローブカードとの間を接続してロックする第2のロック機構40のロック状態を検出するアンロック側センサ30およびロック側センサ31と、それぞれのロック状態に基づいて、第1のロック機構10と第2のロック機構40とのシーケンスの制御を行うシーケンス制御部32と、を備えている。

(もっと読む)

試験装置

【課題】半導体ウエハの両面よりプローブを接触させて各半導体チップの特性を試験する試験装置において、所望の温度に半導体ウエハを加熱して各半導体チップを試験することができる試験装置を提案する。

【解決手段】両面にプローブを接触可能に半導体ウエハを保持し、この半導体ウエハの両面をそれぞれヒータ部により加熱し、この両面にそれぞれプローブを接続して当該半導体ウエハに設けられた半導体チップを試験する。

(もっと読む)

半導体集積回路の故障解析装置及び故障解析方法

【課題】電源電圧や電源電流の変化が微小であり、通常のOBIRCH法では解析が困難な故障を解析する半導体集積回路の故障解析装置、方法を提供する。

【解決手段】半導体集積回路の出力端子の電圧を測定する電圧測定部と、半導体集積回路の内部回路であって出力端子に接続される内部回路の状態を設定するテストパターンを半導体集積回路に与えるテストパターン発生部と、レーザービームを内部回路の所定の領域に対して走査しながら照射し、照射された部分の抵抗値を変化させるレーザー走査部と、レーザー走査部及び電圧測定部と連動し、レーザービームを照射したときに、出力端子の電圧の変化したレーザービームの照射位置を検出して表示する故障位置表示部と、を備える。

(もっと読む)

プロトタイプシステムにおける汎用的な可制御性及び可観測性のための方法及び装置

【課題】プロトタイプの試験を行うための方法及びシステムを提供することである。

【解決手段】この方法は、第1のインタフェース・コンポーネントにおいて、ユーザ設計の少なくとも一部及び関連付けられた検証モジュールを表す構成画像に関連付けられた構成パラメータと、ランタイム制御情報とを受信することを含む。この方法は、さらに、第1のインタフェース・コンポーネントを使用して、構成画像をデバイスへ送信することを含む。第2のインタフェース・コンポーネントは、第1のインタフェース・コンポーネントから受信された構成画像及びランタイム制御情報のうち少なくとも1つに基づいて、タイミング及び制御情報を検証モジュールへ送信するように構成され得る。第2のインタフェース・コンポーネントからタイミング及び制御情報を受信することに応答して、検証モジュールは、デバイスを制御し、且つ/又は、ユーザ設計の少なくとも一部のデバイス状態を監視する。

(もっと読む)

半導体試験装置

【課題】複数のドライバのタイミングを校正するときに、高い精度のタイミング校正を行うことを目的とする。

【解決手段】本発明の半導体試験装置は、DUT1に信号を出力するドライバ10およびドライバ10に接続されるコンパレータ11とドライバ10のタイミングを校正するために設けた基準コンパレータ6との間の校正経路Lに信号を反射する複数の半導体スイッチ15が設けられる半導体試験装置2であって、コンパレータ11がドライバ10から出力されて基準コンパレータ6で反射した校正信号を検出するときに、半導体スイッチ15で多重反射した反射信号が校正信号の検出に干渉しないように、校正経路Lを基準コンパレータ6が分割した各分割経路L1〜L3の電気長Tpd1〜Tpd3を設定している。

(もっと読む)

検査データと組み合わせて設計データを使用するための方法及びシステム

【課題】検査データと組み合わせて設計データを使用するためのさまざまな方法及びシステムが実現される。

【解決手段】設計データ空間における検査データの位置を決定するための一コンピュータ実施方法は、ウェハ上のアライメント部位に対する検査システムにより取り込まれたデータを所定のアライメント部位に対するデータにアラインさせることを含む。この方法は、さらに、設計データ空間における所定のアライメント部位の位置に基づいて設計データ空間におけるウェハ上のアライメント部位の位置を決定することを含む。それに加えて、この方法は、設計データ空間におけるウェハ上のアライメント部位の位置に基づいて設計データ空間における検査システムによりそのウェハについて取り込まれた検査データの位置を決定することを含む。一実施形態では、検査データの位置は、サブピクセル精度で決定される。

(もっと読む)

半導体試験装置および半導体試験装置のタイミング校正方法

【課題】複数のドライバのタイミングを校正するときに、高い精度のタイミング校正を行うことを目的とする。

【解決手段】本発明の半導体試験装置は、DUT1に信号を出力する複数のドライバ10を備える半導体試験装置2であって、ドライバ10のタイミングを校正するための基準コンパレータ6にドライバ10からの信号を入力したときの波形が変化する間の第1の時間T1とドライバ10の出力端での信号の波形が変化する間の第2の時間T2とに基づいてドライバ10のタイミングを校正する校正値を補正する補正部25を備えている。これにより、伝送損失による波形なまりの影響を除去でき、校正値を補正して、ドライバのタイミング校正を高い精度で行うことができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】一つのTEGで複数方向の位置ずれを検出できるようにする。

【解決手段】この半導体装置は、TEG300を有している。TEG300は、プラグ及び配線のいずれか一方である第1要素と、プラグ及び配線の他方である第2要素を有している。第2要素は、互いに異なる方向から第1要素に面しており、第1要素から離間している。本実施形態において、第1要素はプラグ320であり、第2要素は配線330である。プラグ320は、コンタクトであってもよいし、ビアであってもよい。またプラグ320は、配線330の上に位置していてもよいし、下に位置していてもよい。

(もっと読む)

プローブカードの配線基板調整治具及び配線基板修正方法並びに配線基板調整治具を用いて調整されたプローブカードを用いた検査方法及び検査システム

【課題】プローブ針の針先平面度を高い精度で調整し、負圧による撓みを抑えて正確な検査を行う。

【解決手段】接続ユニットが、ポゴピンブロックと、ポゴピンブロック支持部とを有し、プローブカードが、複数のプローブ針が装着された配線基板と、上記配線基板を支持して上記配線基板の上記ポゴピンブロック側を負圧に保つ配線基板支持部と、上記負圧に抗して上記配線基板を支持するアンカーとを有する上記検査装置の、上記プローブ針の針先平面度を修正する配線基板調整治具である。上記ポゴピンブロックに設けられたポゴピン装着穴と、当該ポゴピン装着穴に装着されたポゴピンと、上記配線基板の上記ポゴピンブロック側を負圧にする吸引手段とを備え、上記吸引手段で真空引きして実際の検査使用時の上記配線基板の変形を再現する。また、他の発明は上記配線基板調整治具を用いた配線基板修正方法並びに検査方法及び検査システムである。

(もっと読む)

半導体試験装置、波形表示方法および波形表示プログラム

【課題】波形を生成するまでの時間を長くすることなく波形の表示精度を高精度化することを目的とする。

【解決手段】本発明の半導体試験装置1は、DUT2から出力される電圧が測定範囲MR内にあるか否かを判定する判定部12を備える半導体試験装置1であって、電圧の最小値Vminから最大値Vmaxまでの間を設定された電圧分割数VDで分割したときの単位電圧VUの1.5倍を測定範囲MRとして、この測定範囲MRを単位電圧VUごとにシフトさせる制御を判定部12に対して行う判定制御部23と、判定部12の判定結果に基づいて、電圧の波形を生成する波形生成部25と、を備えることを特徴としている。

(もっと読む)

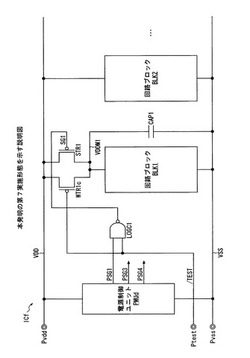

半導体集積回路

【課題】半導体集積回路に設けられた任意の機能ブロックに電源を供給する電源スイッチのテストを高速化する。

【解決手段】電源スイッチの構成として、電源供給レールおよび機能ブロックの間に直列に接続された2つのトランジスタを用いる。これら2つのトランジスタの導通状態は、独立して制御可能とする。2つのトランジスタの間の接点に観測ノードを設ける。電源スイッチのテストの結果を検出するための観測ノードにおける容量を小さくすることで、観測ノードにおける電圧変化が安定するまでの時間を短縮することが可能となる。

(もっと読む)

モニタリング装置及びモニタリングシステム

【課題】LSI等の不具合発生時の原因追求を容易化する。

【解決手段】LSI内又はLSIの近傍にモニタリング装置100を配置し、モニタリング装置100内で、周波数カウンタ20が、一定時間でのリングオシレータ10の発振周波数を計測し、計測した発振周波数を示す発振周波数情報を生成し、時刻カウンタ30が、周波数カウンタ20により発振周波数が計測された時刻を示す時刻情報を生成し、出力制御部80が、発振周波数情報と時刻情報とを対応付けて記憶装置90に出力し、記憶装置90が、発振周波数情報と時刻情報をログとして記憶する。これにより、LSIが起動してから不具合発生までの間の発振周波数の推移を観測することで遅延の相対的な変化を確認することができ、LSIの個体差を気にする必要がなく、不具合発生時の原因追求を容易化できる。

(もっと読む)

半導体試験装置

【課題】試験時間に大きな影響を与えることなく、校正により半導体試験の精度を向上させる。

【解決手段】試験対象の半導体デバイスにテスト信号を出力するための切替可能な複数の経路と、経路の切替を指示する設定命令ブロックとテスト信号出力を指示する信号出力命令ブロックとを含んだテストユニットを1または複数個備えたテストプログラムを実行する制御部と、テストプログラムのテストユニット実行中において、設定命令ブロックの実行後、信号出力命令ブロックの実行前に、設定命令ブロックで設定された経路における校正データを取得し、取得した校正データを用いて、信号出力命令ブロックに基づいて出力されるテスト信号の補正を行なう校正処理部とを備えた半導体試験装置。

(もっと読む)

半導体検査装置、及び荷電粒子線の画像、或いは光学条件の選択装置

【課題】本発明は、光学条件の調整を容易に行うことを目的とする半導体検査装置等の提供を目的とする。

【解決手段】上記目的を達成するために、荷電粒子線装置を備えた半導体検査装置、或いは荷電粒子線装置の画像,光学条件選択装置であって、異なる複数の光学条件にて得られた画像データと、設計データに基づいて形成される画像データとの間でマッチングを行い、当該マッチングに基づいて、前記光学条件、或いは画像の選択を行う半導体検査装置、或いは荷電粒子線装置の画像,光学条件選択装置を提案する。

(もっと読む)

水冷式半導体試験装置の冷却水タンク

【課題】水冷式半導体試験装置の冷却水を貯蔵する冷却水タンクにおいて、配管内の結露を起因とする水位上限オーバーフロー誤検出を防止する。

【解決手段】側面に水位上限を定める開口部が設けられた冷却水タンク本体と、開口部によりタンク本体内部と連結したサブタンクと、水位上限を超えた冷却水を、サブタンクを経由して外部に排出する排出用配管とを備え、サブタンクは、開口部より高い位置において外気開放され、底面が開口部より低い位置にある水冷式半導体試験装置の冷却水タンク。

(もっと読む)

微細回路用フレキシブル・スペース・トランスフォーマ・アセンブリ

【課題】

プローブ・ヘッドをプリント回路基板に電気的に相互接続するためのスペース・トランスフォーマを提供する。

【解決手段】

第1の面にテスト・デバイスのコンタクト・パッドを、また第2の面にプリント回路基板のコンタクト・パッドを形成されて有する。導電性回路パターンは、テスト・デバイスのコンタクト・パッドとプリント回路基板のコンタクト・パッドとの間に延びている。シム板がフレキシブル多層回路の第1の面の周囲に固定され、また底板がフレキシブル多層回路の第2の面の周囲に固定される。底板は、テスト・デバイスのコンタクト・パッドと揃った底板支柱によって分離され、プリント回路基板のコンタクト・パッドと揃った複数の内部開口を有する。複数の相互接続は、プリント回路基板のコンタクト・パッドに接着および電気的相互接続され内部開口を貫通して延びている。

(もっと読む)

41 - 60 / 1,860

[ Back to top ]